## CM-388L 386SX-40 PC/104 CPU Module

Reference Manual

Revised December 2004

## **Legal Notice**

Square One Industries, Inc. provides no warranty with regard to this manual or other information contained herein and hereby expressly disclaims any implied warranties of merchantability or fitness for any particular purpose with regard to this manual or other such information. In no event shall Square One Industries, Inc. be liable for any incidental, consequential, or special damages arising out of or in connection with this manual or other information contained herein or the use thereof. Square One Industries, Inc. reserves the right to make any modification to this manual or the information contained herein at any time and without notice.

# Contents

| Introduction<br>1.1<br>1.2                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                       | Infiguration       7         Jumpers / Connectors Quick Reference       7         Component Locations       8         Keyboard Connector (K/B)       9         Mouse Connector (MOUSE)       9         Floppy Disk Drive Connector (FDC)       9         COM Port B Connector (RS-232) (COMB)       10         COM Port B Connector (RS-485) (CN1)       10         COM Port A Connector (RS-232) (COMA)       10         Hard Disk Active LED (HDLED)       10         Single +5V Input (POWER)       10         IDE Connector (IDE)       11         VGA Connector (VGA)       11         LCD Connector (LCD)       12         System Reset Connector (RST)       12         Printer Connector (LPT)       13         Buzzer (BZ)       13         CMOS Battery Clear Jumper (JP1)       13         LCD Panel Voltage Select (JP2)       13         COM B RS-232/422/485 Select (JP3)       13         M-Systems DiskOnChip SSD Socket (JP4)       13 |

| DiskOnChip I<br>3.1<br>3.2<br>3.3                     | Flash Disk SSD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Watchdog Ti<br>4.1<br>4.2                             | mer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AMI BIOS Se<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6 | Starting Setup       20         Main Menu       21         Standard CMOS Setup       23         Advanced CMOS Setup       26         Advanced Chipset Setup       28         Peripheral Setup       30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.7<br>5.8                                  | Change Supervisor Password                                                                                                                                               |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCD/VGA Displa<br>6-1                       | ay                                                                                                                                                                       |

| Appendix A: Exp<br>A-1                      | PC/104 Pin Assignments                                                                                                                                                   |

| Appendix B: Ted<br>B-1<br>B-2<br>B-3<br>B-4 | chnical Summary       37         Interrupt Map       37         Timer & DMA Channel Maps       37         RTC & CMOS RAM Map       38         Memory & I/O Maps       39 |

| Appendix C: Tre<br>C-1<br>C-2<br>C-3        | Troubleshooting                                                                                                                                                          |

Introduction 1

#### 1.1 Specifications

- CPU: ALI M6117D single chip with on-chip 386SX-40 CPU.

- MEMORY: 4MB soldered on board.

- CMOS Backup: CMOS Back up by Li battery.

- BIOS: AMI 128KB Flash BIOS EPROM.

- KEYBOARD/ MOUSE CONNECTORS: Supports 5-pin PS/2 and PC/AT Keyboard and PS/2 Mouse Connector.

- BUS TYPE: PC/104 Connector.

- WATCHDOG: Programmable 30.5 us ~ 512 sec.

- LCD/VGA: HMC HM 86508 LCD/VGA chip with 1MB Display memory, supports CRT and 24-bit TFT/DSTN/EL LCD flat panel

- IDE INTERFACE: One port supports up to 2 IDE devices.

- FLOPPY DISK DRIVE INTERFACE: Supports up to two Floppy Disk Drives, 3.5" or 5.25" FDD (360K/720K/1.2M/1.44M/2.88M) Drives A, B swappable.

- Serial Port x 2: 16-byte FIFO 16C550 serial port, jumper selectable RS- 232 x 1 + RS-232/422/485 x 1.

- Parallel Port: One bi-directional parallel port configurable as LPT1, 2, 3 supports IEEE1284 compliant high-speed EPP and ECP modes.

- Speaker: Buzzer on Board.

- System Power Requirement: Single +5V power by using 2-pin power connector.

- Operating Temperature: 0~60°C

- Board Dimensions: 96mm x 90mm

- Board Weight: 0.1Kg.

## 1.2 Safety Precautions

Follow the warnings below to protect your system from damage and yourself from injury:

- 1. Avoid exposing your system to static electricity at any time.

- 2. Protect yourself from electric shock. Do not touch any components of this board when the power is ON. Always disconnect power when the system is not in use.

- 3. Disconnect power when you change any hardware devices.

## Hardware Configuration

### 2.1 Jumpers / Connectors Quick Reference

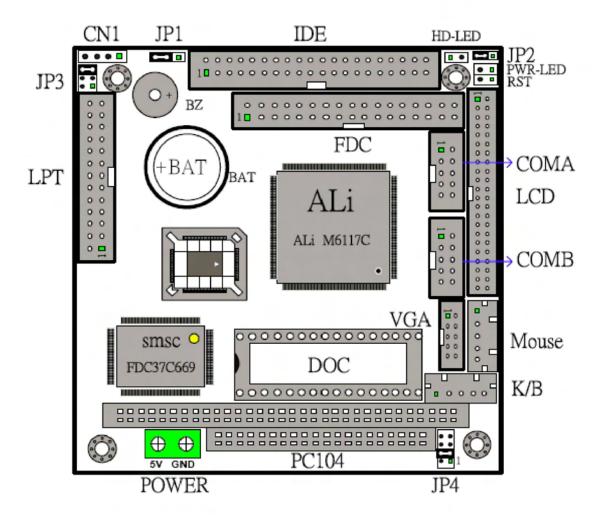

JSP 5-pin AT K/B Connector K/B 5-Pin PS/2 Mouse Connector MOUSE Floppy Disk Drive Connector FDC COMB RS-232 COM Port B Connector (10 pin) RS-485 COM Port B Connector (2 pin) CN1 COM Port A (RS-232) COMA Hard Disk Active LED **HDLED** Single +5V Input **POWER** IDE Hard Disk Driver Connector IDE **VGA** Connector **VGA** LCD LCD Connector System Reset Switch **RST** M-Systems DiskOnChip SSD Socket DOC **Printer Connector** LPT **CMOS Battery Clear Jumper** JP1 LCD Panel Voltage Connector JP2 RS-232/485 Selector JP3 **DOC Address Select** JP4 Power LED **PWRLED**

### 2.2 Component Locations

## 2.3 Keyboard Connector (K/B)

| PIN | ASSIGNMENT | PIN | ASSIGNMENT |

|-----|------------|-----|------------|

| 1   | CLK        | 2   | DATA       |

| 3   | NC         | 4   | GND        |

| 5   | VCC        |     |            |

## 2.4 Mouse Connector (MOUSE)

| PIN | ASSIGNMENT | PIN | ASSIGNMENT |

|-----|------------|-----|------------|

| 1   | CLK        | 2   | DATA       |

| 3   | NC         | 4   | GND        |

| 5   | VCC        |     |            |

## 2.5 Floppy Disk Drive Connector (FDC)

| PIN | ASSIGNMENT | PIN | ASSIGNMENT |

|-----|------------|-----|------------|

| 1   | GND        | 2   | RPM        |

| 3   | GND        | 4   | NC         |

| 5   | GND        | 6   | NC         |

| 7   | GND        | 8   | INDEX      |

| 9   | GND        | 10  | MTR0       |

| 11  | GND        | 12  | DRV1       |

| 13  | GND        | 14  | DRV0       |

| 15  | GND        | 16  | MTR1       |

| 17  | GND        | 18  | DIR        |

| 19  | GND        | 20  | STEP       |

| 21  | GND        | 22  | WDATA      |

| 23  | GND        | 24  | WGATE      |

| 25  | GND        | 26  | TRK0       |

| 27  | GND        | 28  | WRTPRT     |

| 29  | MID1       | 30  | RDATA      |

| 31  | GND        | 32  | SEL        |

| 33  | MID0       | 34  | DSKCHG     |

### 2.6 COM Port B Connector (RS-232) (COMB)

| PIN | ASSIGNMENT | PIN | ASSIGNMENT |

|-----|------------|-----|------------|

| 1   | DCD        | 2   | RXD        |

| 3   | TXD        | 4   | DTR        |

| 5   | GND        | 6   | DSR        |

| 7   | RTS        | 8   | СТЅ        |

| 9   | RI         | 10  | NC         |

## 2.7 COM Port B Connector (RS-485) (CN1)

| PIN | ASSIGNMENT | PIN | ASSIGNMENT |

|-----|------------|-----|------------|

| 1   | Data+      | 2   | Data-      |

## 2.8 COM Port A Connector (RS-232) (COMA)

| PIN | ASSIGNMENT | PIN | ASSIGNMENT |

|-----|------------|-----|------------|

| 1   | DCD        | 2   | RXD        |

| 3   | TXD        | 4   | DTR        |

| 5   | GND        | 6   | DSR        |

| 7   | RTS        | 8   | CTS        |

| 9   | RI         | 10  | NC         |

## 2.9 Hard Disk Active LED (HDLED)

| PIN | ASSIGNMENT | PIN | ASSIGNMENT |

|-----|------------|-----|------------|

| 1   | VCC        | 2   | GND        |

## 2.10 Single +5V Input (POWER)

| PIN | ASSIGNMENT    | PIN | ASSIGNMENT |

|-----|---------------|-----|------------|

| 1   | +5V           | 2   | GND        |

| 3   | +12V (Option) |     |            |

## 2.11 IDE Connector (IDE)

| PIN | ASSIGNMENT | PIN | ASSIGNMENT |

|-----|------------|-----|------------|

| 1   | RESET      | 2   | GND        |

| 3   | HD7        | 4   | HD8        |

| 5   | HD6        | 6   | HD9        |

| 7   | HD5        | 8   | HD10       |

| 9   | HD4        | 10  | HD11       |

| 11  | HD3        | 12  | HD12       |

| 13  | HD2        | 14  | HD13       |

| 15  | HD1        | 16  | HD14       |

| 17  | HD0        | 18  | HD15       |

| 19  | GND        | 20  | NC         |

| 21  | DREQ       | 22  | GND        |

| 23  | IOW        | 24  | GND        |

| 25  | IOR        | 26  | GND        |

| 27  | IOCHRDY    | 28  | ALE        |

| 29  | DACK       | 30  | GND        |

| 31  | IRQ        | 32  | IO16       |

| 33  | SA1        | 34  | NC         |

| 35  | SA0        | 36  | SA2        |

| 37  | HDCS0      | 38  | HDCS1      |

| 39  | DASP       | 40  | GND        |

## 2.12 VGA Connector (VGA)

| PIN | ASSIGNMENT | PIN | ASSIGNMENT |

|-----|------------|-----|------------|

| 1   | RED        | 2   | GND        |

| 3   | GREEN      | 4   | GND        |

| 5   | BLUE       | 6   | GND        |

| 7   | H-SYNC     | 8   | GND        |

| 9   | V-SYNC     | 10  | GND        |

## 2.13 LCD Connector (LCD)

| PIN | ASSIGNMENT | PIN | ASSIGNMENT |

|-----|------------|-----|------------|

| 1   | +12V       | 2   | +12V       |

| 3   | GND        | 4   | GND        |

| 5   | +5V        | 6   | +5V        |

| 7   | FPVEE      | 8   | GND        |

| 9   | P0         | 10  | P1         |

| 11  | P2         | 12  | P3         |

| 13  | P4         | 14  | P5         |

| 15  | P6         | 16  | P7         |

| 17  | P8         | 18  | P9         |

| 19  | P10        | 20  | P11        |

| 21  | P12        | 22  | P13        |

| 23  | P14        | 24  | P15        |

| 25  | P16        | 26  | P17        |

| 27  | P18        | 28  | P19        |

| 29  | P20        | 30  | P21        |

| 31  | P22        | 32  | P23        |

| 33  | GND        | 34  | GND        |

| 35  | SHFCLK     | 36  | FLM        |

| 37  | M          | 38  | LP         |

| 39  | GND        | 40  | ENABLK     |

| 41  | GND        | 42  | NC         |

| 43  | +5V        | 44  | 5V         |

## 2.14 System Reset Connector (RST)

| PIN | ASSIGNMENT | PIN | ASSIGNMENT |

|-----|------------|-----|------------|

| 1   | SIGNAL     | 2   | GND        |

## 2.15 Printer Connector (LPT)

| PIN | ASSIGNMENT | PIN | ASSIGNMENT |

|-----|------------|-----|------------|

| 1   | STROB      | 2   | AUTOFD     |

| 3   | PD0        | 4   | ERROR      |

| 5   | PD1        | 6   | INIT       |

| 7   | PD2        | 8   | SLCTIN     |

| 9   | PD3        | 10  | GND        |

| 11  | PD4        | 12  | GND        |

| 13  | PD5        | 14  | GND        |

| 15  | PD6        | 16  | GND        |

| 17  | PD7        | 18  | GND        |

| 19  | ACK        | 20  | GND        |

| 21  | BUSY       | 22  | GND        |

| 23  | PE         | 24  | GND        |

| 25  | SLCT       | 26  | GND        |

## 2.16 Buzzer (BZ)

| PIN | ASSIGNMENT | PIN | ASSIGNMENT |

|-----|------------|-----|------------|

| 1   | VCC        | 2   | SIGNAL     |

## 2.17 CMOS Battery Clear Jumper (JP1)

1-2 ON: Clear CMOS 2-3 ON: Default

## 2.18 LCD Panel Voltage Select (JP2)

1-2 ON: +5V 2-3 ON: +3.3V

### 2.19 COM B RS-232/422/485 Select (JP3)

1-2 ON: RS-232 Enabled. 2-3 ON: RS-422/485 Enabled.

### 2.20 M-Systems DiskOnChip SSD Socket (JP4)

| ADDRESS   | JUMPER SETTING |         |         |         |  |  |

|-----------|----------------|---------|---------|---------|--|--|

| SELECTION | PIN 1&2        | PIN 3&4 | PIN 5&6 | PIN 7&8 |  |  |

| C000      | ON             | OFF     | OFF     | OFF     |  |  |

| C800      | OFF            | ON      | OFF     | OFF     |  |  |

| D000      | OFF            | OFF     | ON      | OFF     |  |  |

| D800      | OFF            | OFF     | OFF     | ON      |  |  |

## DiskOnChip Flash Disk SSD

3

#### 3.1 Preface

The CM-388 features a 32-pin socket to support the M-Systems DiskOnChip FlashDisk SSD. The DiskOnChip can be built on board by order. The DiskOnChip Flash Disk should be mapped into an 8K byte window in the BIOS expansion address space of the CM-388 PC/104 CPU Module which is usually located in the address range 0C8000H to 0DE000H. The CM-388 can contain the operating system in the DiskOnChip to allow systems to boot without a hard disk.

The DiskOnChip can run standard MS-DOS and the board can boot from the DiskOnChip, which is fully DOS Command compatible. Users can read and write DOS commands and data to DiskOnChip in the same manner as using a hard disk drive.

Users can set this DiskOnChip as a physical HDD and its priority is software selectable. For example, if a system has one HDD, either the HDD or the DiskOnChip could be assigned as C or D Drive.If the system has no HDD, the DiskOnChip will default as C drive. When it is set as C drive, it can boot the system as if using a hard disk drive. The data capacities of DiskOnChip are 2MB, 4MB, 8MB, 12MB, 24MB, 40MB, 72MB, and 144MB.The location of the M-Systems DiskOnChip socket is U10.

#### 3.2 Quick Installation Guide

- 1. Make sure the CM-388/389 PC/104 Module has power OFF

- 2. Plug the DiskOnChip chip into socket U10. Verify the direction is correct (pin1 of the DiskOnChip is aligned with pin1 of the U10 socket).

- 3. Power ON the system.

- 4. Go to BIOS Setup "Advanced Chipset Setup"

| 5. | GPCS Function       | Εn | ıa | ble  |    |      |

|----|---------------------|----|----|------|----|------|

|    | GPCS0 Command       | ME | ΞΝ | MR/W | /  | 8bit |

|    | GPCS0 Start Address | 0C | 8  | 000  |    | HEX  |

|    | GPCS0 Size          | 8  |    | KBY  | ΓΙ | E    |

(1) GPCS0 Command Always MEMR/W 8bit

(2) GPCS0 Start Address It's between C8000H ...... DE000H

(3) GPCS0 Size Always 8 KBYTE

Save the Settings and reboot the computer.

- 6. During POST, you should see a message displayed by the DiskOnChip SSD when its drivers are loaded into the system's memory.

- 7.If the DiskOnChip SSD is the only disk in the system, it will appear as the first disk (Drive C: in DOS)

- 8. The DiskOnChip can be used immediately via the "Format" procedure.

### 3.3 Utility Reference

For additional information regarding the M-Systems DiskOnChip, visit M-Systems at http://www.m-sys.com.

# Watchdog Timer

4

## 4.1 Setting Watchdog Timer Function

INDEX 37H: Enable/Disable watchdog

Bit 7: counter read mode.

| Bit | Value | Action                                                                                                                                            |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-5 | X     | Do not modify of these bits!                                                                                                                      |

| 6   | 0     | Disable Watchdog Timer                                                                                                                            |

|     | 1     | Enable Watchdog Timer                                                                                                                             |

| 7   | 0     | When read from index 3Bh,3Ah,39h;the return value is the setting counter value.                                                                   |

|     | 1     | When bit 7 set from 0 to 1, the counter present value will be latched to buffer. When read from 3Bh,3Ah,39h;the return value is the buffer value. |

| Bit | Value | Action       |

|-----|-------|--------------|

| 7-4 | 0000  | Reserved     |

|     | 0001  | IRQ3         |

|     | 0010  | IRQ4         |

|     | 0011  | IRQ5         |

|     | 0100  | IRQ6         |

|     | 0101  | IRQ7         |

|     | 0110  | IRQ9         |

|     | 0111  | IRQ10        |

|     | 1000  | IRQ11        |

|     | 1001  | IRQ12        |

|     | 1010  | IRQ14        |

|     | 1011  | IRQ15        |

|     | 1100  | NMI          |

|     | 1101  | System Reset |

|     | 1110  | Reserved     |

|     | 1111  | Reserved     |

| 3-0 | Х     | Reserved     |

### INDEX 39H, 3AH, 3BH: Watchdog timer

| Index   | 3Bh   | 3Ah   | 39H   |

|---------|-------|-------|-------|

| Bits    | D7 D0 | D7 D0 | D7 D0 |

| Counter | [ MSB |       | LSB]  |

### Example:

| Index | 3Bh | 3Ah | 39H | Time Out  |

|-------|-----|-----|-----|-----------|

|       | 00h | 00h | 01h | 30.5 µsec |

|       | 00h | 00h | 02h | 61 µsec   |

|       | 00h | 00h | 03h | 91.5 µsec |

|       | 00h | 01h | 00h | 7.8 msec  |

|       | 00h | 02h | 00h | 15.6 msec |

|       | 00h | 03h | 00h | 23.4 msec |

|       | 01h | 00h | 00h | 2 sec     |

|       | 02h | 00h | 00h | 4 sec     |

|       | 03h | 00h | 00h | 6sec      |

|       | FFh | FFh | FFh | 512 sec   |

#### INDEX 3CH: Time out status & Reset

| Bit | Value | Action                   | Meaning   |

|-----|-------|--------------------------|-----------|

| 4~0 | Х     | Do not modify these bits |           |

| 5   | 0     | No meaning               |           |

|     | 1     | Reset timer              |           |

| 6   | Х     | Х                        |           |

| 7   | 0     | Not (yet) occurred       | Read only |

|     | 1     | Has occurred             |           |

#### 4.2 Watchdog Program Example

The I/O port 22h is the index register and I/O port 23h is the data register. To read a configuration register, write the index value to I/O port 22h,then read data from I/O port 23h.

To write a configuration register, write the index value to I/O port 22h, then write data to I/O port 23h.

Example 1: If we want to read the data of a configuration register with an index of 10h, the steps are:

- 1) Write 10h (index) to I/O port 22h

- 2) Read data from I/O port 23h

Example 2: If we want to write data 55h to a configuration register with an index of 12h, the steps are:

- 1) Write 12h (index) to I/O port 22h

- 2) Write data 55h to I/O port 23h

Example 3: The steps of locking/unlocking the configuration registers:

```

OUT 22h, 13h (Enable 13h)

OUT 23h, C5h (Unlock)

OUT 22h, XXh (XX = Configuration Index)

OUT 23h, YYh (YY = Configuration data)

OUT 22h, Xxh

OUT 23h, YYh (Configuration can be written repeatedly)

OUT 22h, 13h (Enable 13h)

OUT 23h, 00h (Lock)

```

#### Example 4: Enable WatchDog

- ; Please use TASM to compile the following program.

- ; Execute under DOS environment.

- ; .286

- .model smart

- .code

- Start proc c

- mov ax,0c513h ; Unlock config register

- call writechip

- mov ax,3737h ; Disable watchdog timer

- call readchip and al,10111111b

- and al, lullillib

- xchg ah,al

- call writechip

- mov ax,083bh ; Set the expected counter value

- call writechip ; to [080000h]

- mov ax,003ah ; 30.5usc \* 080000h = 16sec

- call writechip mov ax,0039h call writechip

- Square One Industries, Inc. www.square1industries.com

```

mov ax,3838h

; Select "System reset " as timeout action

call readchip

and al,00001111b

or al,11010000b

xchg ah,al

call writechip

mov ax,3737h

; Enabled watchdog timer

or al,01000000b

xchg ah,al

call writechip

mov ax,0013h

; Lock config register

mov writechip

mov ax,4c00h

int 21h

endp

readchip proc c

out 22h,al

nop

nop

in al,23h

nop

nop

writechip proc c

out 22h,al

nop

nop

xchg ah,al

out 23h,al

nop

nop

xchg ah,al

ret

endp

end

```

#### Example 5: Reset Watchdog

mov ax,0c513h ; Unlock configuration register call writechip mov ax,3c3ch ; Reset watchdog timer counter call readchip or al,00100000b ; The counter is reset at out 23h,al xchg ah,al call writechip mov ax,0013h ; Lock configuration register call writechip

## AMI BIOS Setup

#### 5.1 Starting Setup

The AMI BIOS is immediately activated when the computer starts to power on. The BIOS reads the system information contained in the CMOS and starts the process of checking out the system and configuring it. When it finishes, the BIOS will seek an operating system on one of the disks and then launch and turn control over to the operating system.

While the BIOS is in control, the Setup program can be activated in one of two ways:

- 1. Press the <Del> key immediately after switching the system on, or

- 2. Press the <Del> key when the following message appears briefly at the bottom of the screen during the POST (Power On Self Test).

Press DEL to enter SETUP.

If the message disappears before you respond and you still wish to enter Setup, restart the system to try again by turning it OFF then ON or pressing the "RESET" button on the system case. You may also restart by simultaneously pressing <Ctrl>, <Alt>, and <Delete> keys. If you do not press the keys at the correct time and the system does not boot, an error message will be displayed and you will again be asked to...

PRESS F1 TO CONTINUE, DEL TO ENTER SETUP

#### 5.2 Main Menu

Once you enter the AMI BIOS CMOS Setup Utility, the Main Menu will appear on the screen. The Main Menu allows you to select from several setup functions and two exit choices. Use the arrow keys to select among the items and press <Enter> to accept and enter the sub-menu.

# AMIBIOS HIFLEX SETUP UTILITY - VERSION 1.23 (C) 1999 American Megatrends, INC. All Rights RESERVED

Standard CMOS Setup

Advanced CMOS Setup

Advanced Chipset Setup

PCI / Plug and Play Setup

Peripheral Setup

Auto-Detect Hard Disks

Change User Password

Change Supervisor Password

Change Language Setting

Auto Configuration with Optimal Settings

Auto Configuration with Fail Safe Settings

Save Settings and Exit

Exit Without Saving

Standard CMOS setup for changing time, date, hard disk type, etc. ESC:Exit ↑ ↓ : Sel F2/F3: Color F10: Save & Exit

Note that a brief description of each highlighted selection appears at the bottom of the screen.

#### Setup Items:

The main menu includes the following main setup categories. Please note that some systems may not include all entries.

- **Standard CMOS Setup**: This setup includes all the items in a standard AT-compatible BIOS.

- Advanced CMOS Setup: This setup includes all the items of AMI special enhanced features.

- Advanced Chipset Setup: Change Boot from (Floppy, IDE 0..., , CDROM),

Floppy Drive Swap, etc..., Password Check, or just to Setup.

- PCI / Plug and Play Setup: This item appears if the system supports PnP/ISA.

- Peripheral Setup: This setup specifies settings for integrated peripherals.

- Auto-Detect Hard Disks: Automatically detect and configure hard disk parameters. See also Section 5.3 "Standard CMOS Setup".

- Change Supervisor Password: Changes, sets, or disables password. It allows

the user to limit access to the system and Setup.

- Save Settings and Exit: Saves CMOS value changes to CMOS and exit setup.

- Exit Without Saving: Abandon all CMOS value changes and exit setup.

#### 5.3 Standard CMOS Setup

The items in the Standard CMOS Setup Menu are divided into 10 categories. Each category includes none, one or more than one setup items. Use the arrow keys to highlight the item and then use the <PgUp> or <PgDn> keys to select the desired value for each item.

AMIBIOS SETUP - STANDARD CMOS SETUP (C) 1999 American Megatrends, INC. All Rights Reserved Date (mm/dd/yyyy):Wed Jan 09, 2002 Base Memory: 640KB Extd Memory: 3 MB Time (hh/mm/ss): 10:56:28 Floppy Drive A: 1.44 MB 3½ Floppy Drive B: Not Installed LBA Blk PIO 32Bit Size Cyln Head Wpcom Sec Mode Mode Type Mode Mode Pri Master : Auto Off Pri Slave : Auto Off Sec.Master: Not Installed Sec.Slave : Not Installed Boot Sector Virus Protection Disabled Month: Jan - Dec **ESC:Exit** ↑ ↓ :Sel Day : 01 - 31 PgUp/PgDn: Modify Year: 1901 - 2099 F2/F3:Color

- Date: The date format is <day>, <date> <month> <year>. Press<F3> to show

the calendar.. The input range for the Month is 1-12. Range for Date is 1-31 or

the maximum allowed for the specific month. Range for Year is 1900-2099.

System BIOS will calculate the day of the week automatically.

- **Time**: The time format is <hour> <minute> <second>. The time is calculated based on the 24-hour military-time clock. For example, 1 p.m. is 13:00:00.

- Daylight saving: The category adds one hour to the clock when daylight-saving time begins. Italso subtracts one hour when standard time returns. Available settings are Enabled/Disabled.

- Primary Master / Slave: The categories identify the types of 1 channels that

have been installed in the computer. There are 45 predefined types and 4 user

definable types are for Enhanced IDE BIOS. Type "1" to Type "45" are

predefined. Type "user" is user-definable.

Press PgUp or PgDn to select a numbered hard disk type or type the number and press <Enter>. Note that the specifications of your drive must match with the drive table. The hard disk will not work properly if you enter improper information for this category.

If your hard disk drive type is not matched in the list, you can use Type"User" to define your own drive type manually.

If you select Type "User", you will need to know the information listed below. Enter the information directly from the keyboard and press <Enter>. This information should be included in the documentation from your hard disk vendor or the system manufacturer.

If the controller of HDD interface is ESDI, the selection should be "Type 1".If the controller of HDD interface is SCSI, the selection should be "None".If you select Type "Auto", BIOS will automatically detect the HDD & CD-ROM Drive at the POST stage and showing the IDE for HDD & CD-ROM Drive.

| TYPE    | Drive type          |

|---------|---------------------|

| CYLS    | Number of cylinders |

| HEADS   | Number of heads     |

| WPCOM   | Write precom        |

| SECTORS | Number of sectors   |

| MODE    | Mode type           |

If a hard disk has not been installed select NONE and press <ENTER>

Drive A Type / Drive B Type: The category identifies the types of Floppy Disk

Drive A or Drive B that have been installed in the computer.

| None        | No floppy drive installed.                           |  |  |

|-------------|------------------------------------------------------|--|--|

| 360K, 5.25" | 5¼" PC-type standard drive; 360K byte capacity.      |  |  |

| 1.2M, 5.25" | 5¼" AT-type high-density drive; 1. 2M byte capacity. |  |  |

| 720K, 3.5"  | 3½" double-sided drive; 720K byte capacity.          |  |  |

| 1.44M, 3.5" | 3½" double-sided drive; 1.44M byte capacity.         |  |  |

| 2.88M, 3.5" | 3½" double-sided drive; 2.88M byte capacity.         |  |  |

• Virus Protection: When this item is enabled, the AMI BIOS will monitor the boot sector and partition table of the hard disk drive for any attempt on modification. If an attempt is made, the BIOS will halt the system and the following error message will appear. If necessary, you will be able to run an anti-virus program to locate and remove the problem before any damage is done.

NOTE: Many disk diagnostic programs which attempt to access the boots ector table can cause the above warning message. If you will be running such a program, we recommend that it better for you to disable the Virus Protection beforehand.

- Memory: System memory is displayed as determined by POST.

- Base Memory: The POST will determine the amount of base (or conventional)

memory installed in the system. The value of the base memory is typically 512K

for systems with only 512K memory installed on the motherboard, or 640K for

systems with 640K or more memory installed on the motherboard.

- **Extended Memory**: The BIOS determines how much extended memory is present during the POST. This is the amount of memory located above 1MB in the CPU's memory address map.

#### 5.4 Advanced CMOS Setup

This section allows the user to configure the system for advanced operations. One can select the system's default speed, boot-up sequence, shadowing, keyboard operation and security.

| AMIBIOS SETUP – ADVANCED CMOS SETUP<br>© 1999 American Megatrends, INC . All Right Reserved                                                                                                                                                                                                        |                                                                                                                   |                                                                                      |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|

| Quick Boot 1st Boot Device 2nd Boot Device 3rd Boot Device Try Other Boot Devices BootUp Num-Lock Floppy Drive Swap Floppy Drive Seek PS/2 Mouse Support System Keyboard Primary Display Password Check Wait For 'F1' If Error C000, 32k Shadow C800, 32k Shadow D000, 32k Shadow D800, 32k Shadow | Enabled Floppy IDE-0 SCSI Yes On Disabled Disabled Enabled Absent Absent Setup Enabled Disabled Disabled Disabled | Available Options Disabled ► Enabled  ESC:Exit ↑ ↓:Sel PgUp/PgDn:Modify F2/F3: Color |  |  |

- 1st (2nd, 3rd) Boot Device: Selects Boot device and sequence.

- Try Other Boot Devices: If Yes, BIOS will try to boot from other Boot Devices if all Selected Boot Devices failed to boot. If NO, BIOS will try to Boot from only the Selected Boot Devices.

- BootUp Num-Lock: This allows you to determine the default status of the numeric keypad. By default, the system boots up with NumLock on.

- Floppy Drive Swap: When enabled, physical drive A will be assigned to logical drive B, and physical drive B will be assigned to logical drive A.

- Boot Up Floppy Seek: The system will detect and verify operation of the floppy drive type.

- Mouse Support: This item will set PS/2 Mouse as Enabled or Disabled.

- System Keyboard: This item can set System Keyboard as Absent or Present.

- Primary Display: The category selects the type of video adapter used for the primary system monitor. Although secondary monitors are supported, you do not

have to select the type in Setup.

- Password Check: You can select whether the password is required every time the system boots or only when you enter the Setup. You can assign "Supervisor Password" and "User Password" in the main CMOS Setup Utility Screen.

- Wait For "F1" if Error: AMI BIOS POST error messages are followed by:

Press <F1> to continue If this option is set to Disabled, AMI BIOS does not wait for you to press the <F1> key after an error message. The settings are Disabled or Enabled. The Optimal and Fail-Safe default settings are Enabled.

C000 - C800, 32K Shadow / D000 - D800, 32K Shadow / E000 - E800, 32K

Shadow: Optional firmware will be copied from ROM to RAM when this option is enabled.

#### 5.5 Advanced Chipset Setup

| AMIBIOS SETUP – ADVANCED CMOS SETUP<br>© 1999 American Megatrends, INC. All Right Reserved                                                                                                                                                                                                                                              |                                                                                                                     |                                                                                              |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|

| AT Bus Clock Slow Refresh Memory Hole At 15-16M RAS Precharge time RAS Active Time Insert Wait CAS Precharge Time Insert Wait Memory Write Insert Wait Memory Miss Read Insert Wait ISA Write cycle end Insert Wait I/O Recovery I/O Recovery Period On – Chip I/O Recovery 16Bit ISA Insert Wait WatchDog Timer WatchDog Signal Select | 14.318/2 15 us Disabled 1.5T Disable Disable Disable Enabled Enabled 0.75 us Disable Enabled Disable Enabled System | Available Options  14.318/2  PCLK2/3  PCLK2/4  PCLK2/5  PCLK2/6  PCLK2/8  PCLK2/10  PCLK2/12 |  |  |

|                                                                                                                                                                                                                                                                                                                                         |                                                                                                                     | ESC:Exit ↑ ↓ :Sel<br>PgUp/PgDn :Modify<br>F2/F3 : Color                                      |  |  |

- AT BUS Clock: ISA Bus Clock timing selection. When Auto Configuration is Disabled, then14.318/2, Pclk2/3, Pclk2/4, Pclk2/5, Pclk2/6, Pclk2/8, Pclk2/10, Pclk2/12 isavailable on ISA Bus.

- Slow Refresh: The chipset refresh settings deal with the timing of CPU access to dynamic random access memory (DRAM). The default timing has been carefully chosen and should only be altered if data is being lost. Such a scenario might occur if your system had mixed speed DRAM chips installed so that greater delays may be required to preserve the integrity of the data held in the slower memory chips. Available values: 120us, 60us, 15us.

- Memory Hole At 15-16M: Use this option to specify an area in memory that cannot be addressed on the ISA bus. The settings are Disabled, 512-640K, or 15-16MB. The default setting is Disabled.

- RAS Precharge time: DRAM must continually be refreshed otherwise it will lose its data. Normally, DRAM is refreshed entirely as the result of a single request. This option allows you to determine the number of CPU clocks allocated for the Row Address Strobe to accumulate its charge before the DRAM is refreshed. If insufficient time is allowed, refresh may be incomplete and data will be lost. Available values: 3.5T, 2.5T, 1.5T.

- RAS Active Time Insert Wait: When it is enabled, the system will insert a wait state for lower speed DRAM.

- Memory Miss Read Insert Wait: The above four items are disabled by default.

- I/O Recovery: This item allows you to determine the recovery time allowed for 8 bit I/O.Choices are 0u, 0.25u to 3.05 CPU clocks. Default is 1 clock.

- I/O Recovery Period: The recovery time is the length of time, measured in CPU clocks, which the system will delay after the completion of an input/output request. This delay takes place because the CPU is operating so much faster than the input/output bus that the CPU must be delay to allow of the completion of the I/O.

- WatchDog Function: Watchdog can be set through BIOS.

- WatchDog Signal: Set IRQ3, 4 ,5 ,6 ,7 ,9 ,10 ,11 ,12 ,14 ,15 ,NMI , Reset.

- WatchDog Timer: Set Timer 1, 2, 4, 8, 16, 32, 64, 128, 256, 512 sec.

### 5.6 Peripheral Setup

| AMIBIOS SETUP – PERIPHERAL SETUP<br>© 1999 American Megatrends, INC. All Right Reserved |                                       |                   |  |  |  |  |

|-----------------------------------------------------------------------------------------|---------------------------------------|-------------------|--|--|--|--|

| Onboard IDE                                                                             | Onboard IDE Primary Available Options |                   |  |  |  |  |

| Onboard FDD                                                                             | Auto                                  | ▶ Disable         |  |  |  |  |

| Onboard Serial Port1                                                                    | 3F8h/COM1                             | Primary           |  |  |  |  |

| Onboard Serial Port2                                                                    | 2F8h/COM2                             | Secondary         |  |  |  |  |

| Serial Port2 Mode                                                                       | Normal                                |                   |  |  |  |  |

| Receiver Polarity                                                                       | Non-Inverted                          |                   |  |  |  |  |

| Transmitter Polarity                                                                    | Non-Inverted                          | l .               |  |  |  |  |

| Onboard Serial Port3                                                                    | Disabled                              | 1                 |  |  |  |  |

| Serial Port3 IRQ                                                                        | N/A                                   | 1                 |  |  |  |  |

| Onboard Serial Port4                                                                    | N/A                                   | 1                 |  |  |  |  |

| Serial Port4 Mode                                                                       | N/A                                   | 1                 |  |  |  |  |

| Serial Port4 IRQ                                                                        | N/A                                   | 1                 |  |  |  |  |

| Receiver Polarity                                                                       | N/A                                   | 1                 |  |  |  |  |

| Transmitter Polarity                                                                    | N/A                                   |                   |  |  |  |  |

| Onboard Parallel Port                                                                   | 378                                   | 1                 |  |  |  |  |

| Parallel Port Mode                                                                      | ECP                                   |                   |  |  |  |  |

| EPP Version                                                                             | N/A                                   |                   |  |  |  |  |

| Parallel Port IRQ                                                                       | 5                                     | ESC:Exit ↑ ↓:Sel  |  |  |  |  |

| Parallel Port DMA Channel                                                               | 3                                     | PgUp/PgDn :Modify |  |  |  |  |

| Onboard Parallel Port2                                                                  | Disabled                              | F2/F3 : Color     |  |  |  |  |

- Onboard IDE: This item allows you to select the base address and IRQ for HDD active mode. Disabled and Primary are selectable. This setup item allows you to either enable or disable the primary controller.

- Onboard FDC Controller: This is to enable or disable the onboard Floppy controller.

- Onboard Serial Port 1 / 2: These items specify the base I/O port address and IRQ for the onboard Serial Port 1 (COM 1)/ Serial Port 2 (COM 2). Available addresses include 3F8h, 2F8h, 3E8h, 2E8h.

- Onboard Parallel Port: This specifies the base I/O port address and IRQ of the onboard Parallel Port. Settings are 378, 278, and 3BC.

#### 5.7 Change Supervisor Password

User can set either supervisor or user password, or both of them. The differences between them are: 'supervisor password' can enter and change the options of the setup menus and 'user password' just can enter but does not have the right to change the options of the setup menus.

When one selects this function, the following message will appear at the center of the screen to assist in creating a password:

#### ENTER PASSWORD:

Type the password, up to eight characters in length, and press <Enter>. The password typed now will clear any previously entered password from CMOS memory. User will be asked to confirm the password. Type the password again and press <Enter>. One may also press <Esc> to abort the selection and not enter a password.

To disable a password, just press <Enter> when user is prompted to enter the password. A message will confirm the password will be disabled. Once the password is disabled, the system will boot and Setup can be entered freely.

#### PASSWORD DISABLED

When a password has been enabled, user will be prompted to enter it upon attempting to enter Setup. This prevents an unauthorized person from changing any part of the system configuration. Additionally, when a password is enabled, one can also require the BIOS to request a password every time the system is rebooted. This would help prevent unauthorized use of the computer. User can determine when the password is required within the BIOS Features Setup Menu and its Security option. If the Security option is set to "System", the password will be required both at boot and at entry to Setup. If set to "Setup", prompting only occurs when trying to enter Setup.

## 5.8 Drive Type Table

| Туре | Size<br>(MB) | Cyln | Head | Sec | Wpcom | LBA | BLK | PIO  | 32BIT |

|------|--------------|------|------|-----|-------|-----|-----|------|-------|

| 1    | 10           | 306  | 4    | 17  | 128   | Off | Off | Auto | Off   |

| 2    | 20           | 615  | 4    | 17  | 300   | Off | Off | Auto | Off   |

| 3    | 30           | 615  | 6    | 17  | 300   | Off | Off | Auto | Off   |

| 4    | 62           | 940  | 8    | 17  | 512   | Off | Off | Auto | Off   |

| 5    | 46           | 940  | 6    | 17  | 512   | Off | Off | Auto | Off   |

| 6    | 20           | 615  | 4    | 17  | 65535 | Off | Off | Auto | Off   |

| 7    | 30           | 462  | 8    | 17  | 256   | Off | Off | Auto | Off   |

| 8    | 30           | 733  | 5    | 17  | 65535 | Off | Off | Auto | Off   |

| 9    | 112          | 900  | 15   | 17  | 65535 | Off | Off | Auto | Off   |

| 10   | 20           | 820  | 3    | 17  | 65535 | Off | Off | Auto | Off   |

| 11   | 35           | 855  | 5    | 17  | 65535 | Off | Off | Auto | Off   |

| 12   | 49           | 855  | 7    | 17  | 65535 | Off | Off | Auto | Off   |

| 13   | 20           | 306  | 8    | 17  | 128   | Off | Off | Auto | Off   |

| 14   | 42           | 733  | 7    | 17  | 65535 | Off | Off | Auto | Off   |

| 16   | 20           | 612  | 4    | 17  | 300   | Off | Off | Auto | Off   |

| 17   | 40           | 977  | 5    | 17  | 300   | Off | Off | Auto | Off   |

| 18   | 56           | 977  | 7    | 17  | 65535 | Off | Off | Auto | Off   |

| 19   | 59           | 1024 | 7    | 17  | 512   | Off | Off | Auto | Off   |

| 20   | 30           | 733  | 5    | 17  | 300   | Off | Off | Auto | Off   |

| 21   | 42           | 733  | 7    | 17  | 300   | Off | Off | Auto | Off   |

| 22   | 30           | 733  | 5    | 17  |       | Off | Off | Auto | Off   |

| 23   | 10           | 306  | 4    | 17  | A     | Off | Off | Auto | Off   |

| 24   | 53           | 925  | 5    | 17  | 65535 | Off | Off | Auto | Off   |

| 25   | 69           | 925  | 9    | 17  | 65535 | Off | Off | Auto | Off   |

| 26   | 43           | 754  | 7    | 17  | 754   | Off | Off | Auto | Off   |

| 27   | 68           | 754  | 11   | 17  | 65535 | Off | Off | Auto | Off   |

| 28   | 40           | 699  | 7    | 17  | 256   | Off | Off | Auto | Off   |

| 29   | 68           | 823  | 10   | 17  | 65535 | Off | Off | Auto | Off   |

| 30   | 53           | 918  | 7    | 17  | 918   | Off | Off | Auto | Off   |

| 31   | 93           | 1024 | 11   | 17  | 65535 | Off | Off | Auto | Off   |

| 32   | 127          | 1024 | 15   | 17  | 65535 | Off | Off | Auto | Off   |

| 33   | 42           | 1024 | 5    | 17  | 1024  | Off | Off | Auto | Off   |

| 34   | 10           | 612  | 2    | 17  | 128   | Off | Off | Auto | Off   |

| 35   | 76           | 1024 | 9    | 17  | 65535 | Off | Off | Auto | Off   |

| 36   | 68           | 1024 | 8    | 17  | 512   | Off | Off | Auto | Off   |

| 37    | 40  | 615  | 8  | 17 | 128   | Off | Off | Auto | Off |

|-------|-----|------|----|----|-------|-----|-----|------|-----|

| 38    | 24  | 987  | 3  | 17 | 987   | Off | Off | Auto | Off |

| 39    | 57  | 987  | 7  | 17 | 987   | Off | Off | Auto | Off |

| 40    | 40  | 820  | 6  | 17 | 820   | Off | Off | Auto | Off |

| 41    | 40  | 977  | 5  | 17 | 977   | Off | Off | Auto | Off |

| 42    | 40  | 981  | 5  | 17 | 981   | Off | Off | Auto | Off |

| 43    | 48  | 830  | 7  | 17 | 512   | Off | Off | Auto | Off |

| 44    | 68  | 830  | 10 | 17 | 65535 | Off | Off | Auto | Off |

| 45    | 144 | 917  | 15 | 17 | 65535 | Off | Off | Auto | Off |

| 46    | 152 | 1224 | 15 | 17 | 65535 | Off | Off | Auto | Off |

| ARMD  |     |      |    |    |       |     |     | Auto | Off |

| CDROM |     |      |    |    |       |     |     | Auto | Off |

| AUTO  |     |      |    |    |       |     |     | Auto | Off |

| USER  |     |      |    |    |       |     |     | Auto | Off |

## LCD/VGA Display

6

#### 6-1 Features

The board uses an HM86508 chip which is an advanced single-chip flat panel and VGA controller. It's used for notebook or portable computer systems with simple operations and powerful features. It contains all functions and supports logic required to implement the IBM VGA display standards and enhanced display modes on LCD, PLASMA, EL panel at register and BIOS level compatible. Also a simultaneous display technology is implemented in HM86508 to be used for CRT and Flat panel.

HM86508 can support flat panel display, resolution up to 1024x768mono, 800x600 hi-color, 640x480 true-color. Unlike on CRT, the pixels on a flat panel display are real, discrete entities of a fixed size. This results in problems when different display modes are mapped onto one panel. The HM86508 provides approach to keep the vertical resolution of the display mode constant but center the active display area vertically on the panel.

The flat panel interface support Monochrome/ Color STN LCD panel, color TFT LCD panel, PLASMA panel and EL panel. Providing direct panel interface to (DD) Dual-panel, Dual-drive for color and monochrome and (SS) Single-panel, Single-drive (supports 8,9,12,15,18,24-bit data). For Single-panel/Single-drive panel which refresh data rate is not high, The HM86508 can set some of the video memory as the frame buffer for panel display to decrease video memory chip counts to one (a 256k x 16DRAM).

The HM86508 serves as a DRAM controller for the display memory, it handles DRAM refresh, display refresh, display memory access by CPU and supply the control signal of DRAM with dual write or dual-cas.

#### Dual-scan STN Frame Buffer:

Shadow Frame Buffer onto display memory for mono or color LCD panel. Pseudo Frame Buffer for color LCD panel (no additional DRAM required). External Frame Buffer for color LCD panel (external additional DRAM required)

#### Enhanced mode includes:

132 x 25 or 132 x 44 text mode

640 x 480/256 colors(Windows accelerations mode support optional)

640 x 480/65536 colors(Windows accelerations mode support optional)

640 x 480/16.8M colors(Windows accelerations mode support optional)

800 x 600/16 colors

800 x 600/256 colors(Windows accelerations mode support optional)

800 x 600/65536 colors(Windows accelerations mode support optional)

800 x 600/16.8M colors

1024 x 768/16 colors

1024 x 768/256 colors(Windows accelerations mode support optional)

1024 x 768/65536 colors(Windows accelerations mode support optional)

1280 x 1024/16 colors(Windows accelerations mode support optional)

1280 x 1024/256 colors (Windows accelerations mode support optional)

1600 x 1280/16 colors interlace display mode

#### • Integrated STN panel support:

Supports Dual/single scan mono STN LCD Panel, up to 64 simultaneous grays. Supports Dual/single scan color STN LCD Panel, up to 64k simultaneous colors, and 61 visual colors .

Provides 8 and 16 bit panel interfaces

#### • Integrated color TFT panel support:

Supports Normal or CRT-like TFT LCD panel Supports 9/12/15 or 18/24 bit panel interface, and up to 16.8M simultaneous colors.

# Appendix A: Expansion Bus

A

## A-1 PC/104 Pin Assignments

| Row D | Pin Name | Row C | Pin Name | Row A | Pin Name | Row B | Pin Name |

|-------|----------|-------|----------|-------|----------|-------|----------|

|       |          |       |          |       |          |       |          |

|       |          |       |          | 1     | IOCHCHK  | 1     | GND      |

|       |          |       |          | 2     | SD7      | 2     | RESETDRV |

|       |          |       |          | 3     | SD6      | 3     | +5V      |

|       |          |       |          | 4     | SD5      | 4     | IRQ9     |

|       |          |       |          | 5     | SD4      | 5     | -5V      |

|       |          |       |          | 6     | SD3      | 6     | DRQ2     |

|       |          |       |          | 7     | SD2      | 7     | -12V     |

|       |          |       |          | 8     | SD0      | 8     | ENDXFR   |

| 1     | GND      | 1     | GND      | 9     | SD1      | 9     | +12V     |

| 2     | MEMCS16  | 2     | SBHE     | 10    | IOCHRDY  | 10    | (KEY)    |

| 3     | IOCS16   | 3     | LA23     | 11    | AEN      | 11    | SMEMW    |

| 4     | IRQ10    | 4     | LA22     | 12    | SA19     | 12    | SMEMR    |

| 5     | IRQ11    | 5     | LA21     | 13    | SA18     | 13    | IOW      |

| 6     | IRQ12    | 6     | LA20     | 14    | SA17     | 14    | IOR      |

| 7     | IRQ15    | 7     | LA19     | 15    | SA16     | 15    | DACK3    |

| 8     | IRQ14    | 8     | LA18     | 16    | SA15     | 16    | DRQ3     |

| 9     | DACK0    | 9     | LA17     | 17    | SA14     | 17    | DACK1    |

| 10    | DRQ0     | 10    | MEMR     | 18    | SA13     | 18    | DRQ1     |

| 11    | DACK5    | 11    | MEMW     | 19    | SA12     | 19    | REFRESH  |

| 12    | DRQ5     | 12    | SD8      | 20    | SA11     | 20    | SYSCLK   |

| 13    | DACK6    | 13    | SD9      | 21    | SA10     | 21    | IRQ7     |

| 14    | DRQ6     | 14    | SD10     | 22    | SA9      | 22    | IRQ6     |

| 15    | DACK7    | 15    | SD11     | 23    | SA8      | 23    | IRQ5     |

| 16    | DRQ7     | 16    | SD12     | 24    | SA7      | 24    | IRQ4     |

| 17    | +5V      | 17    | SD13     | 25    | SA6      | 25    | IRQ3     |

| 18    | MASTER   | 18    | SD14     | 26    | SA5      | 26    | DACK2    |

| 19    | GND      | 19    | SD15     | 27    | SA4      | 27    | TC       |

| 20    | GND      | 20    | (KEY)    | 28    | SA3      | 28    | SALE     |

| •     |          |       |          | 29    | SA2      | 29    | +5V      |

|       |          |       |          | 30    | SA1      | 30    | OSC      |

|       |          |       |          | 31    | SA0      | 31    | GND      |

|       |          |       |          | 32    | GND      | 32    | GND      |

# Appendix B: Technical Summary

B

## B-1 Interrupt Map

| IRQ | ASSIGNMENT                          |

|-----|-------------------------------------|

| 0   | System TIMER interrupt from TIMER-0 |

| 1   | Keyboard output buffer full         |

| 2   | Cascade for IRQ 8-15                |

| 3   | Serial port 2                       |

| 4   | Serial port 1                       |

| 5   | Parallel port 2                     |

| 6   | Floppy Disk adapter                 |

| 7   | Parallel port 1                     |

| 8   | RTC clock                           |

| 9   | Available                           |

| 10  | Available                           |

| 11  | Available                           |

| 12  | Available                           |

| 13  | Math coprocessor                    |

| 14  | Hard Disk adapter                   |

| 15  | Available                           |

## B-2 Timer & DMA Channel Maps

| Timer Channel | Timer Channel          |

|---------------|------------------------|

| 0             | System timer interrupt |

| 1             | DRAM Refresh request   |

| 2             | Speaker tone generator |

| DMA Channel | Assignment                   |

|-------------|------------------------------|

| 0           | Available                    |

| 1           | IBM SDLC                     |

| 2           | Floppy Disk adapter          |

| 3           | Available                    |

| 4           | Cascade for DMA controller 1 |

| 5           | Available                    |

| 6           | Available                    |

| 7           | Available                    |

## B-3 RTC & CMOS RAM Map

| CODE  | ASSIGNMENT                              |

|-------|-----------------------------------------|

| 00    | Seconds                                 |

| 01    | Second alarm                            |

| 02    | Minutes                                 |

| 03    | Minutes alarm                           |

| 04    | Hours                                   |

| 05    | Hours alarm                             |

| 06    | Day of week                             |

| 07    | Day of month                            |

| 08    | Month                                   |

| 09    | Year                                    |

| 0A    | Status register A                       |

| 0B    | Status register B                       |

| 0C    | Status register C                       |

| 0D    | Status register D                       |

| 0E    | Diagnostic status byte                  |

| 0F    | Shutdown byte                           |

| 10    | Floppy Disk drive type byte             |

| 11    | Reserved                                |

| 12    | Hard Disk type byte                     |

| 13    | Reserved                                |

| 14    | Equipment byte                          |

| 15    | Base memory low byte                    |

| 16    | Base memory high byte                   |

| 17    | Extension memory low byte               |

| 18    | Extension memory high byte              |

| 30    | Reserved for extension memory low byte  |

| 31    | Reserved for extension memory high byte |

| 32    | Date Century byte                       |

| 33    | Information Flag                        |

| 34-3F | Reserved                                |

| 40-7F | Reserved for Chipset Setting Data       |

## B-4 Memory & I/O Maps

| MEMORY MAP      | ASSIGNMENT                                          |

|-----------------|-----------------------------------------------------|

| 000000-009FFFF  | System memory used by DOS and applications          |

| 00A0000-00BFFFF | Display buffer memory for VGA/EGA/CGA/MONO adapters |

| 00C0000-00DFFFF | Reserved for I/O device BIOS ROM or RAM buffer.     |

| 00E0000-00EFFFF | Reserved for PCI device ROM                         |

| 00F0000-00FFFFF | System BIOS ROM                                     |

| 0100000-BFFFFFF | System extension memory                             |

| I/O MAP | ASSIGNMENT                             |

|---------|----------------------------------------|

| 000-01F | DMA controller (Master)                |

| 020-021 | Interrupt controller (Master)          |

| 022-023 | Chipset controller registers I/O ports |

| 040-05F | Timer control registers                |

| 060-06F | Keyboard interface controller (8042)   |

| 070-07F | RTC ports & CMOS I/O ports             |

| 080-09F | DMA register                           |

| 0A0-0BF | Interrupt controller (Slave)           |

| 0C0-0DF | DMA controller (Slave)                 |

| 0F0-0FF | Math coprocessor                       |

| 1F0-1F8 | Hard Disk controller                   |

| 278-27F | Parallel port-2                        |

| 2B0-2DF | Graphics adapter controller            |

| 2F8-2FF | Serial port-2                          |

| 360-36F | Network ports                          |

| 378-37F | Parallel port-1                        |

| 3B0-3BF | Monochrome & Printer adapter           |

| 3C0-3CF | EGA adapter                            |

| 3D0-3DF | CGA adapter                            |

| 3F0-3F7 | Floppy disk controller                 |

| 3F8-3FF | Serial port-1                          |

## Appendix C: Troubleshooting

C

### C-1 Troubleshooting POST Messages

During the Power On Self Test (POST), if the BIOS detects an error requiring user action, it will either sound a beep code or display a message. If a message is displayed, it will be accompanied by:

PRESS F1 TO CONTINUE, CTRL-ALT-ESC OR DEL TO ENTER SETUP

#### C-2 Troubleshooting POST Beep

Currently there are two kind of beep codes in BIOS. One code indicates that a video error has occurred and the BIOS cannot initialize the video screen to display any additional information. This beep code consists of a single long beep followed by three short beeps. The other code indicates that a DRAM error has occurred. This beep code consists of a single long repeated beep.

- Error Messages: One or more error messages may be displayed if the BIOS detects an error during the POST. This list includes messages for both the ISA and the EISA BIOS.

- CMOS BATTERY HAS FAILED: CMOS battery is no longer functional. It should be replaced.

- CMOS CHECKSUM ERROR: Checksum of CMOS is incorrect. This can indicate that CMOS has become corrupt. This error may have been caused by a weak battery. Check the battery and replace if necessary.

- DISK BOOT FAILURE, INSERT SYSTEM DISK AND PRESS ENTER: No boot device was found. This could mean that either a boot drive was not detected or the drive does not contain proper system boot files. Insert a system disk into Drive A: and press <Enter>. If the system was expected to boot from the hard drive, make sure the controller is inserted correctly and all cables are properly attached. Also be sure that the disk is formatted as a boot device. Then reboot the system.

- DISKETTE DRIVES OR TYPES MISMATCH ERROR RUN SETUP: Type of diskette drive installed in the system is different from the CMOS definition. Run Setup to reconfigure the drive type correctly.

- DISPLAY SWITCH IS SET INCORRECTLY: Display switch on the motherboard can be set to either monochrome or color. This indicates the switch is set to a different setting than indicated in Setup. Determine which setting is correct, and then turn off the selection.

- DISPLAY TYPE HAS CHANGED SINCE LAST BOOT: Since last power off the system, the display adapter has been changed. User must configure the system for the new display type.

- ERROR ENCOUNTERED INITIALIZING HARD DRIVE: Hard drive cannot be initialized. Be sure the adapter is installed correctly and all cables are correctly and firmly attached. Also be sure the correct hard drive type is selected in Setup.

- ERROR INITIALIZING HARD DISK CONTROLLER: Cannot initialize controller.

Make sure the card is correctly and firmly installed in the bus. Be sure the correct hard drive type is selected in Setup. Also check if any jumper needs to be set correctly on the hard drive.

- FLOPPY DISK CNTRLR ERROR OR NO CNTRLR PRESENT: Cannot find or initialize the floppy drive controller. Make sure the controller is installed correctly and firmly. If there are no floppy drives installed, be sure the Diskette Drive selection in Setup is set to NONE.

- Invalid EISA Configuration: RUN EISA CONFIGURATION UTILITY. The

non-volatile memory containing EISA configuration information was programmed

incorrectly or has become corrupt. Re-run EISA configuration utility to correctly

program the memory.

NOTE: When this error appears, the system will boot in ISA mode, which allows user to run the EISA Configuration Utility.

- KEYBOARD ERROR OR NO KEYBOARD PRESENT: Cannot initialize the keyboard. Make sure the keyboard is attached correctly and no keys are being pressed during the boot. If user is purposely configuring the system without a keyboard, set the error halt condition in Setup to HALT ON ALL, BUT KEYBOARD. This will cause the BIOS to ignore the missing keyboard and continue the boot.

- MEMORY ADDRESS ERROR AT ...: Indicates a memory address error at a specific location. One can use this location along with the memory map for the system to find and replace the bad memory chips.

- MEMORY PARITY ERROR AT ...: Indicates a memory parity error at a specific location. One can use this location along with the memory map for the system to find and replace the bad memory chips.

- MEMORY SIZE HAS CHANGED SINCE LAST BOOT: Memory has been added or removed since the last boot. In EISA mode, use Configuration Utility to reconfigure the memory configuration. In ISA mode, enter Setup and enter the new memory size in the memory fields.

- MEMORY VERIFY ERROR AT ...: Indicates an error verifying a value already written to memory. Use the location along with the system's memory map to locate the bad chip.

- OFFENDING ADDRESS NOT FOUND: This message is used in conjunction with the I/O CHANNEL CHECK and RAM PARITY ERROR messages when the segment that has caused the problem which cannot be isolated.

- OFFENDING SEGMENT: This message is used in conjunction with the I/O CHANNEL CHECK and RAM PARITY ERROR messages when the segment that has caused the problem which has been isolated.

- PRESS A KEY TO REBOOT: This will be displayed at the bottom screen when an error occurs that requires the user to reboot. Press any key and the system will reboot.

- PRESS F1 TO DISABLE NMI, F2 TO REBOOT: When BIOS detects a Nonmaskable Interrupt condition during boot, this will allow the user to disable the NMI and continue to boot, or one can reboot the system with the NMI enabled.

- RAM PARITY ERROR CHECKING FOR SEGMENT ...: Indicates a parity error in Random Access Memory.

- SYSTEM HALTED, (CTRL-ALT-DEL) TO REBOOT ...: Indicates the present boot attempt has been aborted and the system must be rebooted. Press and hold down the CTRL and ALT keys and press DEL.

### C-3 Troubleshooting for POST Codes

NOTE: EISA POST codes are typically output to port address 300h. ISA POST codes are output to port address 80h.

| POST (hex) | Description                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------|

| C2         | NMI is Disabled. Power on delay starting.                                                                       |

| C5         | Power on delay complete. Going to disable cache if any.                                                         |

| C6         | Calculating ROM BIOS checksum.                                                                                  |

| C7         | ROM BIOS checksum passed. CMOS shutdown register test to be done next.                                          |

| C8         | CMOS shutdown register test done. CMOS checksum calculation to be done next.                                    |

| CA         | CMOS checksum calculation done, CMOS Diag byte written CMOS status register about to init for Date and Time.    |

| СВ         | CMOS status register init done. Any initialization before keyboard BAT to be done next.                         |

| CD         | BAT command to keyboard controller is to be issued.                                                             |

| CE         | Keyboard controller BAT result verified. Any initialization after KB controller. BAT to be done next.           |

| CF         | Initialization after KB controller BAT done. Keyboard command byte to be written next.                          |

| D1         | Keyboard controller command byte is written. Going to check pressing of <ins> key during power-on done.</ins>   |

| D2         | Checking for pressing of <ins> key during power-on done. Going to disable DMA and interrupt controller.</ins>   |

| D3         | DMA controller #1, #2, interrupt controller #1, #2 disable. Chipset init/ auto memory detection about to begin. |

| D4         | Chipset initialization/ auto memory detection over. To uncompress the RUNTIME code.                             |

| D5         | RUNTIME code is uncompressed.                                                                                   |

| D0         | Transfer control to uncompressed code in shadow ram atF000: FFF0.                                               |

| 01 | Processor register test about to start and NMI to beDisabled.                                                                                           |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02 | NMI is Disabled. Power-on delay starting.                                                                                                               |

| 03 | Power on delay complete. To check soft reset /power-on.                                                                                                 |

| 05 | Soft reset / power-on determined. Going to disable cache if any.                                                                                        |

| 06 | POST code to be uncompressed.                                                                                                                           |

| 07 | POST code is uncompressed. CPU init and CPU areainit to be done next                                                                                    |

| 08 | CPU and CPU date area init done. CMOS checksum calculation to be done next.                                                                             |

| 09 | CMOS checksum calculation is done, CMOS Diag byte written. CMOS init to begin (if "init CMOS in every boot"is set).                                     |

| 0A | CMOS initialization done (if any).CMOS status register about to init for Date and Time.                                                                 |

| 0B | CMOS status register init done. Any initialization before keyboard BAT to be done next.                                                                 |

| 0C | KB controller I/B free. Going to issue the BAT command to keyboard controller.                                                                          |

| 0E | Keyboard controller BAT result verified. Any initialization after KB controller BAT to be done next.                                                    |

| 0F | Initialization after KB controller BAT done.<br>Keyboard command byte to be written next.                                                               |

| 10 | Keyboard controller command byte is written. Going to issue Pin 23, 24 blocking / unblocking command.                                                   |

| 11 | Pin 23, 24 of keyboard controller is blocked / unblocked.<br>Going to check pressing of <ins> key during power-on.</ins>                                |

| 12 | Checking for pressing of <ins> key during power-on done. Going to disable DMA and interrupt controllers.</ins>                                          |

| 13 | DMA controller #1, #2, interrupt controller #1, #2 disabled.<br>Video display is disabled and port-B is initialized.<br>Chipset init about to begin.    |

| 15 | Chipset initialization over. 8254 timer test about to start.                                                                                            |

| 19 | 8254 timer test over. About to start memory refresh test.                                                                                               |

| 1A | Memory Refresh line is toggling. Going to check 15 micro second ON/OFF time.                                                                            |

| 20 | Memory Refresh period 30 micro second test complete.<br>Base 64K memory to be initialized.                                                              |

| 23 | Base 64K memory initialized. Going to set BIOS stack and to do any setup before interrupt vector init.                                                  |

| 24 | Setup required before interrupt vector initialization complete. Interrupt vector initialized about to begin.                                            |

| 25 | Interrupt vector initialization done. Going to read input port of 8042 for turbo switch (if any) and to clear password if post diagnostic switch is on. |

| 26 | Input port of 8042 is read. Going to initialize global data for turbo switch.                                                                           |

| 0.7 | Olekel dete Seiter Benden franke in 1991 i                                                                                           |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|

| 27  | Global data initialization for turbo switch is over.  Any initialization before setting video mode to be done next.                  |

| 28  | Initialization before setting video mode is complete.  Going for monochrome mode and color mode setting.                             |

| 2A  | Different BUSes init (system, static, output devices) to start if present. (Please see next section for details of different BUSes). |

| 2B  | About to give control for any setup required before optional video ROM check.                                                        |

| 2C  | Processing before video ROM control is done.  About to look for optional video ROM and give control.                                 |

| 2D  | Optional video ROM control is done. About to give control to do any processing after video ROM returns control.                      |

| 2E  | Return from processing after the video ROM control.  If EGA/VGA not found then do display memory R/W test.                           |

| 2F  | EGA/VGA not found. Display memory R/W test about to begin.                                                                           |

| 30  | Display memory R/W test passed. About to look for the retrace checking.                                                              |

| 31  | Display memory R/W test or retrace checking failed. About do alternate display memory R/W test.                                      |

| 32  | Alternate Display memory R/W test passed. About to look for the alternate display retrace checking.                                  |